为什么汽车芯片的算力需求不断提升?为什么7nm车规制程成为高算力车规芯片的必然趋势?国内首款7nm工艺制程高端智能座舱芯片将具备哪些独特性能?

在近期由盖世汽车主办的“2021首届智能汽车域控制器创新峰会”上,芯擎科技产品规划管理部总经理蒋汉平博士发表主题演讲,与线上线下二十多万名与会者共同探讨7nm高性能车规芯片算力趋势。

车企新模式驱动芯片算力创新高

蒋博士系统地阐述了作为高性能智能车规芯片的算力趋势。他认为:芯片算力不断创新高,很大程度上是源于车企对新商业模式的思考。车企现在产生了一个新模式,即在车内进行硬件预埋后,通过OTA软件升级来适配多样化的用户场景和不同安全等级辅助驾驶与自动驾驶功能的逐步迭代,车企不再把算力与不同价位的车型进行硬件平台的分级分步实施,而是先把算力预埋进去,之后再去升级它的功能。同时,车企对算力的要求比我们想象的迭代还要快,也就是在这样背景下,为了满足现有车企客户越来越旺盛、越来越急迫对算力要求,高算力芯片已经成为汽车“新四化”(电动化、网联化、智能化、共享化)的核心驱动力。

高算力车规芯片是电子电气架构快速演变的主赛道

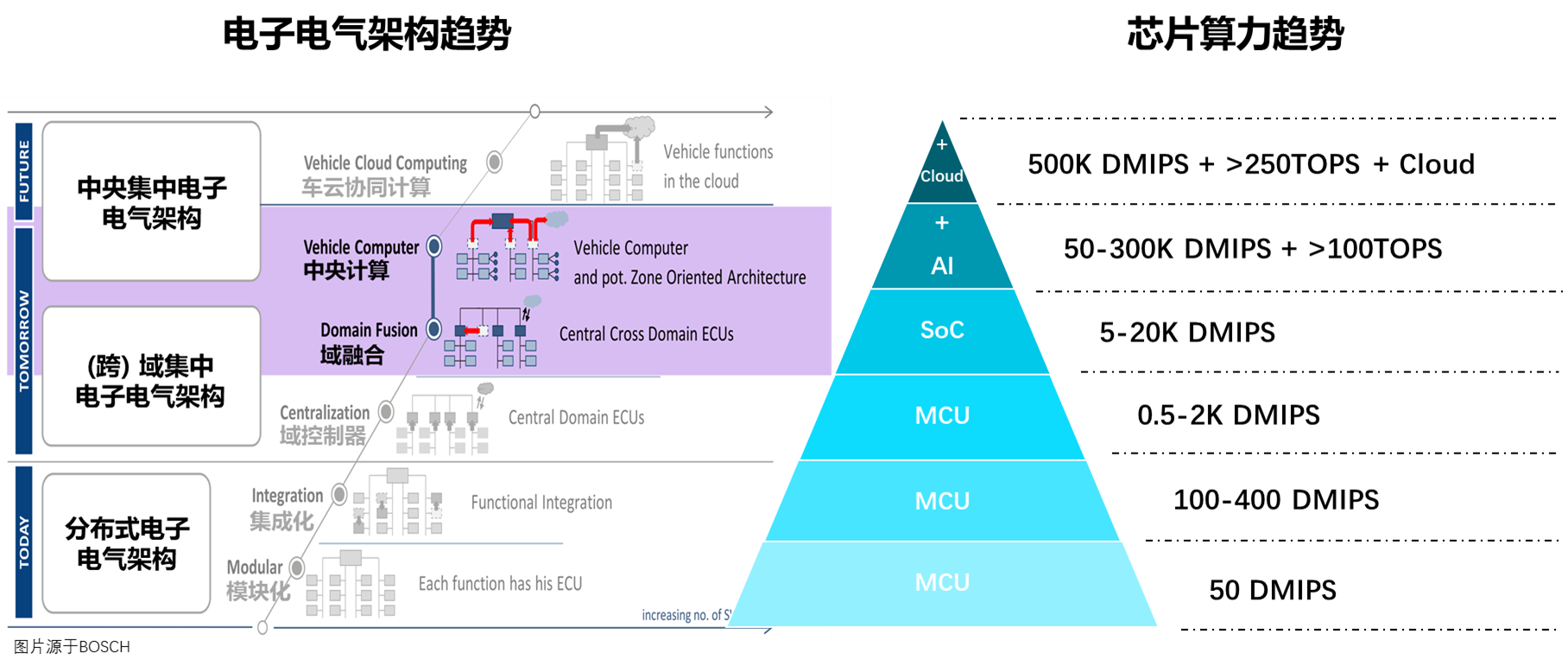

电子电气架构和算力的增长趋势如上图所示。电子电气架构也就是我们常说的E/E架构,实际上定义了车内ECU之间的连接关系和网络拓扑结构。左图是博世公司对汽车电子电气架构趋势的研判,这已成为电子电气架构演变的行业共识。

最下面一层是经典的分布式架构——每个ECU对应一个或者多个功能,各自运行一套独立的软件。这个阶段每个ECU的控制和计算单元基本都是MCU,微控制器,从单一功能MCU到多功能MCU,算力基本在几十到几百DMIPS的量级。完全分布式的架构在应对复杂功能也就是需要多个ECU协同的时候会比较复杂,越多的ECU参与,会成倍增加ECU之间的交互,每个ECU可能分属不同的供应商,运行不同的软件栈,协同和联调的工作非常繁复,所以在传统汽车上增加一个复杂功能是一个非常漫长的过程。为了缓解这种问题,E/E架构引入了“域”的概念,也就是第二层所展示的架构,“域”把相近功能的ECU统一在同一个域控制器底下,这个域内的交互和决策由这个域控制器来完成,这相当于第一个阶段的计算集中化。今天的很多汽车都采用的是这种架构,随着汽车行业以及电子行业的发展,出现了相近域的融合,比如底盘和动力域,这两个域对功能安全和信息安全的要求相近。域控制器对算力的要求相对更高,在这个阶段域控制器也从MCU进化到了CPU,算力基本在1K到小几十K DMIPS的量级。

再上一层是中央计算的架构,这个架构中的中央计算单元会成为全车的最高决策中心,算力进一步集中,基本在几十到几百K DMIPS的量级。另外,无论是娱乐域还是ADAS域,智能化的需求都需要配合不同的硬件加速单元,去做计算密集型的任务。比如,娱乐域需要强大的GPU做图形图像的渲染,3D建模等。再比如自动驾驶需要人工智能的深度学习算法,算力的膨胀速度非常惊人,即便是L3以下级别的辅助驾驶也需要数T到数十TOPS的算力匹配,L3及以上级别的自动驾驶算力需求基本都在上百TOPS。

最上层的云计算架构,需要整个交通基础设施,5G以及车联网生态成熟之后才能慢慢实现,是个非常庞大的系统工程,即便在云计算的架构下一些实时性高的计算也需要本地算力的支撑,并不能完全依赖云端,本地算力依然还是增长的趋势。

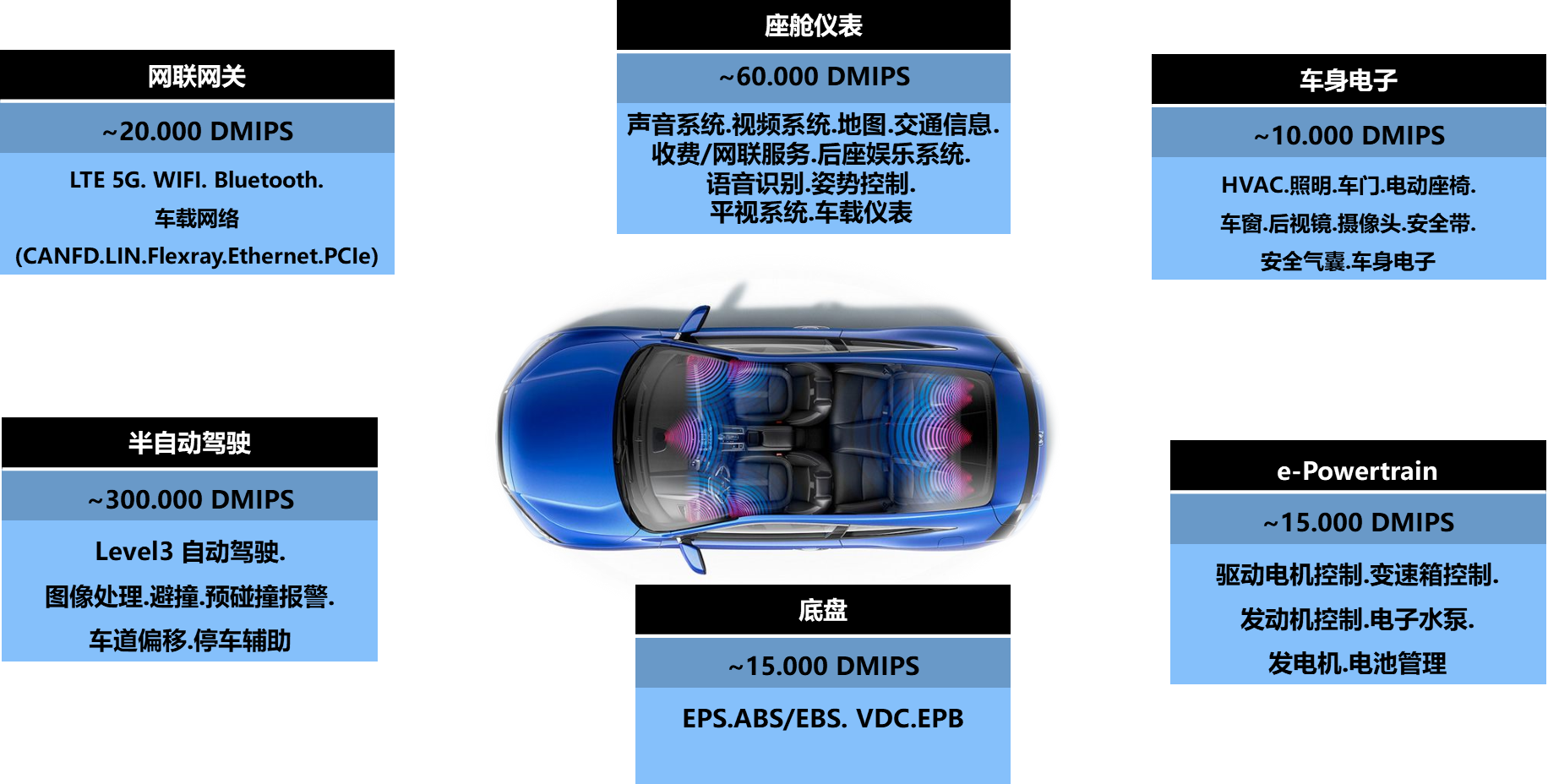

车规芯片算力的差异化实现提高算力预埋的效率

蒋博士同时强调:高算力的预埋需要针对数据类型、应用场景和算法优化,提供差异化的算力实现单元的SOC实现。在典型的SoC中异构计算包含CPU,GPU,DSP和NPU。在处理智能任务时,他们擅长的任务也各不相同。CPU擅长逻辑控制和通用计算,在智能任务方面可以用来做图像的前后处理,多传感器的感知融合,以及最终的决策。GPU拥有非常多的计算单元,擅长做并行计算、图形渲染,也可以用来做图像的前后处理。DSP擅长信号处理,针对不同的场景有音频或者视觉的DSP,可以做语音和视觉的前后处理,也可以做雷达信号处理。NPU主要擅长做大量的矩阵运算,适合用于深度学习比较擅长的领域,比如语音识别、自然语言处理、视觉感知,此外,雷达信号处理现在也出现了很多深度学习的算法。

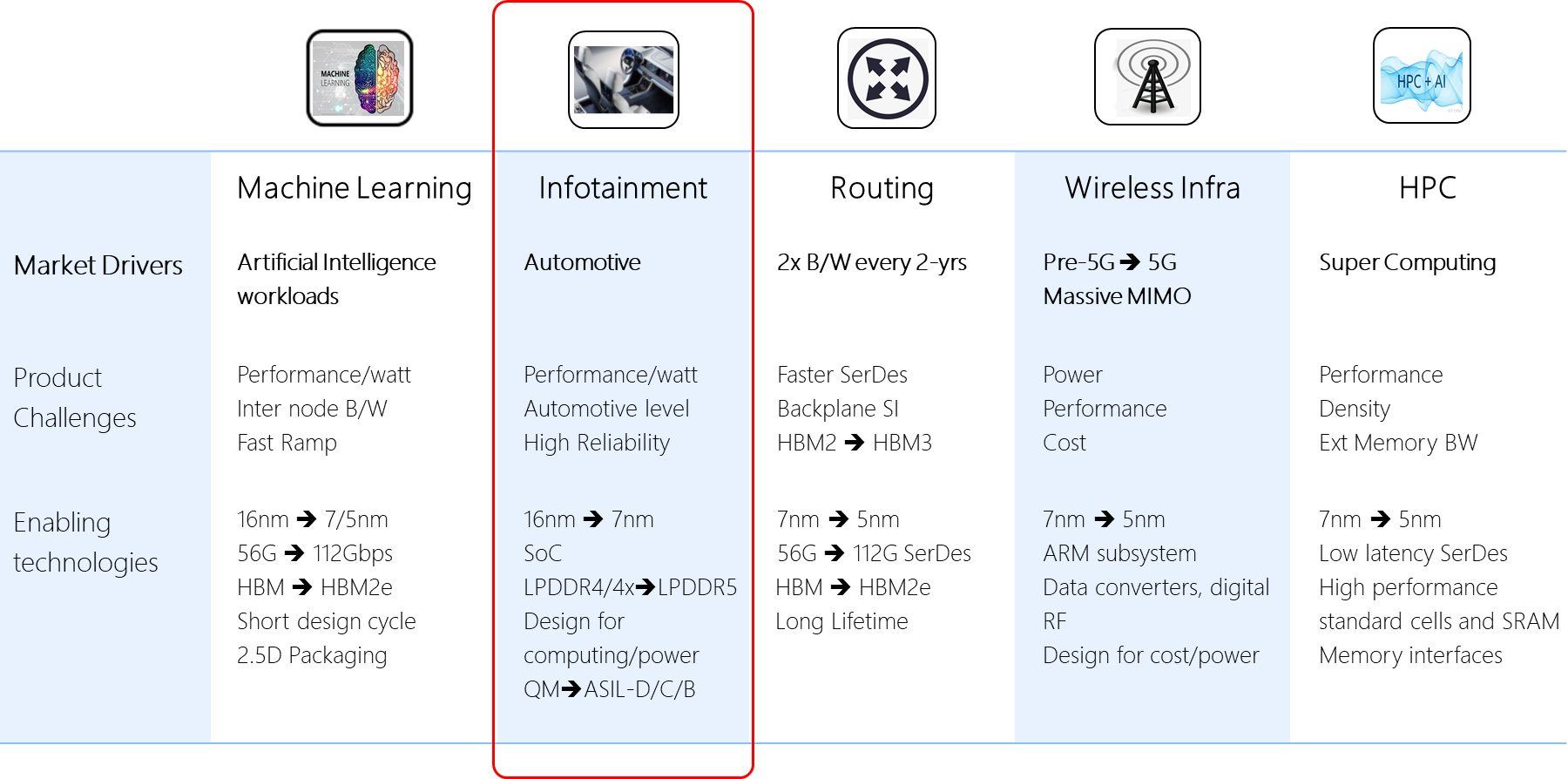

7nm车规制程是高算力车规芯片的必然趋势

7nm工艺的成熟速度是有史以来最快的,技术的亮点更加在于对良率的控制,7nm工艺纷纷被高算力应用领域所使用,相比起16nm节点工艺,7nm可以提供3.3倍的门电路密度,在同等功耗上提供35~40%的速度提升或者可以降低65%的功耗,成本的优势随着生产能力与良率的提升正在快速呈现。

蒋博士给出了主流高算力应用场景的芯片制程演进趋势,并总结了7nm 工艺节点的四大优势:

1、芯片集成度更高。单位面积的晶圆上可以放置更多的逻辑门。同时封装面积变小,节约了晶圆成本和封装成本。进一步节约了成品芯片在单板上所占的面积。使得相同大小的电子产品功能更多,速度更快。

2、芯片耗电量更低。同样大小的逻辑电路做出来,用更先进的工艺会导致耗电量更低。

3、响应速度更快。单管开断速度更快,同样的逻辑电路能够跑到的主频更高,主频高,性能肯定会大幅提升。

4、设计难度更大。为何设计难度大是优点呢?难度高,增加了电子行业的“马太效应”,强者越强,弱者恒弱。护城河加大,行业壁垒增高,后来者难以攀登。

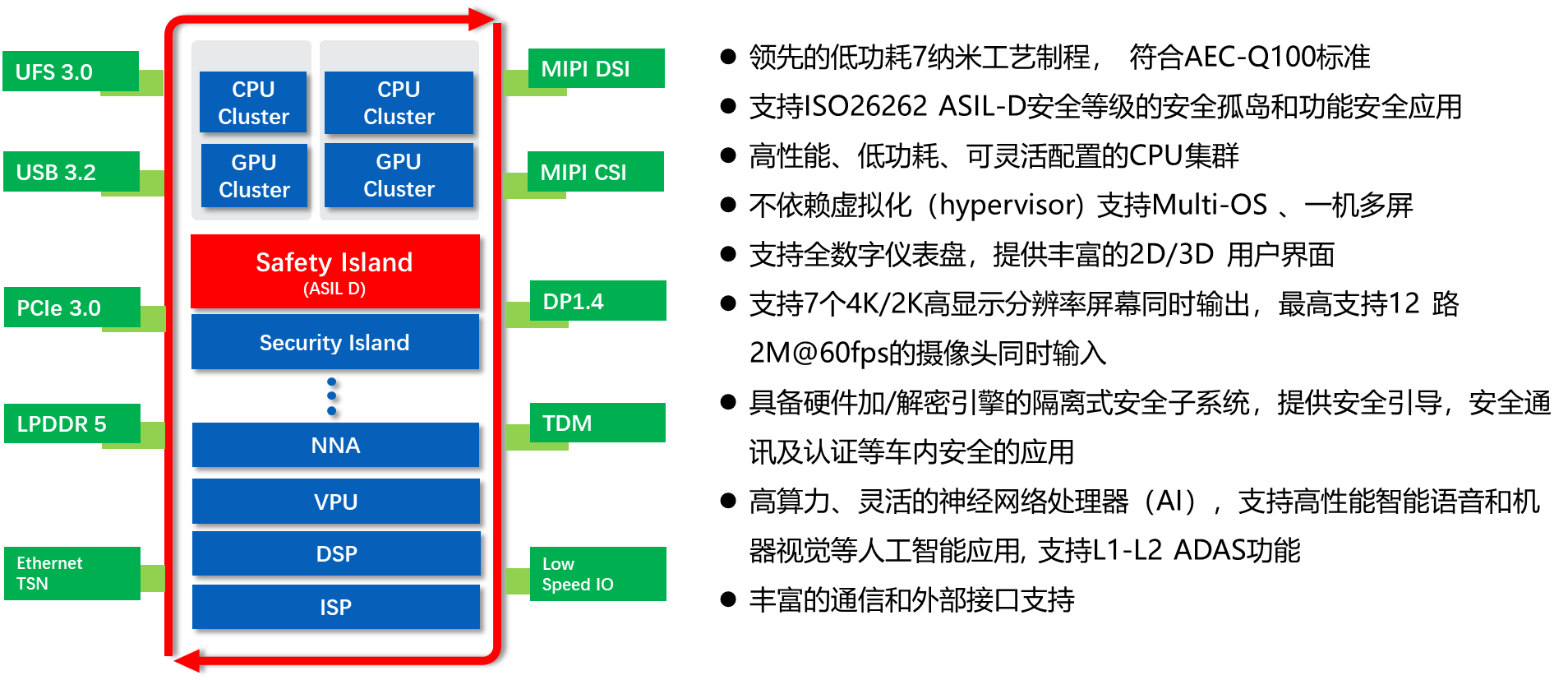

SE1000:国内首款7nm工艺制程高端智能座舱芯片

蒋博士还重点介绍了芯擎在研的车规智能座舱芯片SE1000的规格:SE1000是国内首款7纳米工艺制程高端智能座舱芯片,是采用业界领先的7纳米工艺制程设计的新一代高性能、低功耗车规级智能座舱芯片,赋能日益丰富的车载信息娱乐系统。高性能定制CPU集群,通过面向异构计算而精心设计的SOC系统,可以为用户提供卓越的性能体验。内置高性能嵌入式AI神经网络处理单元,提供更多个性化的智能语音、机器视觉及辅助自动驾驶体验。新一代多核心的图形处理单元,可以动态根据负载进行资源分配;一机多屏多系统,支持多高分辨率屏幕同时输出;内置高性能音频信号处理单元及丰富的音频接口,为用户提供丰富超凡的音视频娱乐体验。

安全性是汽车产品的生命线。芯擎自主开发实现了汽车功能安全(SAFETY)和信息安全体系(SECURITY),并准备通过ISO26262标准认证。该款产品独特的安全孤岛核心(SAFETY ISLAND)为系统提供了冗余和实时的保护,满足汽车芯片对功能安全和信息安全更加严格的标准的要求,为车载应用提供了安全保证。